Huawei sigue trabajando en tecnología parecida al 3DIC para nuevos chips

Huawei podría haber desarrollado una solución 3DIC como respuesta al bloqueo tecnológico impuesto por países occidentales, un paso estratégico que ya estaba contemplado en su planificación y que tiene el potencial de cambiar el rumbo de la situación.

¿En qué consiste esta tecnología y cómo se diferencia de otros chips?

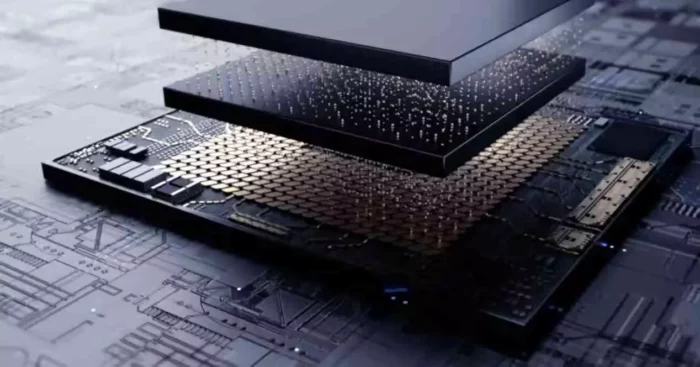

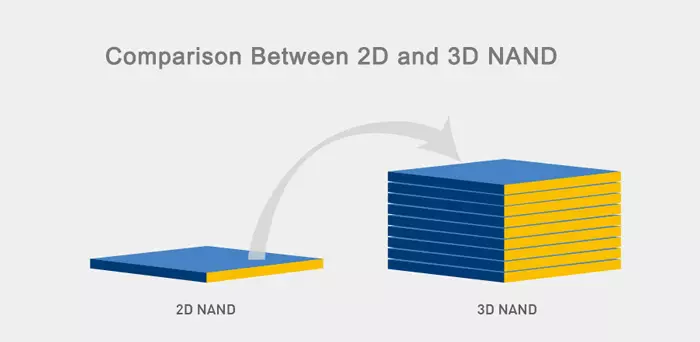

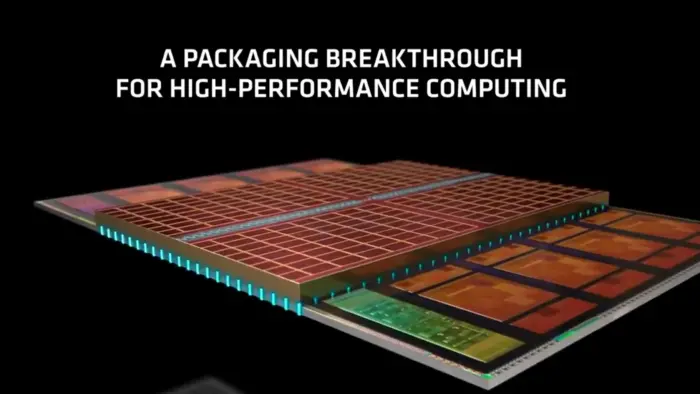

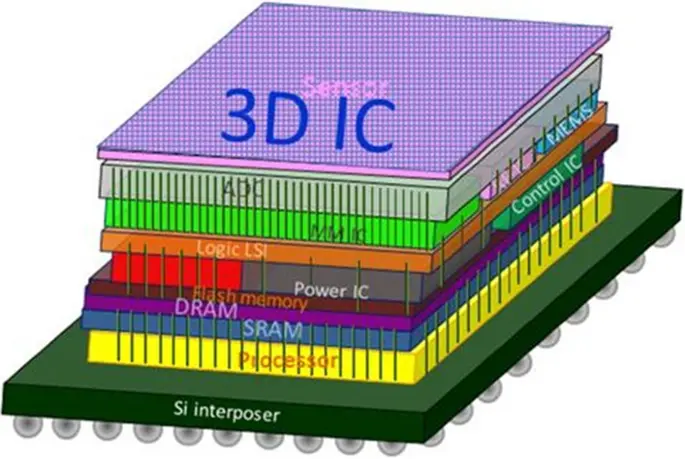

El concepto de tecnología 3DIC no es novedoso: se trata de la disposición de dos o más chips uno encima del otro, estableciendo conexiones verticales entre ellos. Ejemplos anteriores incluyen la tecnología 3D V-Cache de AMD, distintas generaciones de memoria HBM y la memoria 3D-NAND presente en los SSD actuales.

Sin embargo, para Huawei, esta tecnología podría representar la respuesta al veto tecnológico impuesto por Estados Unidos y sus aliados. Cuando se avanza en el desarrollo de una nueva litografía, el objetivo principal es ubicar la máxima cantidad de transistores dentro de un área determinada.

Con la introducción de la tecnología 3DIC, se presenta la oportunidad de incrementar esta capacidad por milímetro cuadrado. En esta evaluación, no se incluye el volumen o milímetro cúbico (mm³), lo que implica que, al apilar múltiples chips diferentes, la densidad por área se incrementará.

En otras palabras, sin necesidad de recurrir a un nuevo nodo de fabricación, se logra la construcción de sistemas más intrincados.

Desde el 2022, era conocido que Huawei estaba trabajando en una solución 3DIC, como respuesta a la restricción impuesta por Estados Unidos, que impedía a la multinacional china acceder a tecnologías de 7 nm o superiores.

En específico, su enfoque consiste en apilar dos chips de 14 nm uno encima del otro, con el objetivo de alcanzar una densidad equivalente a la tecnología de 7 nm en el mismo espacio. Esto les permitiría continuar el desarrollo de chips más sofisticados.

Quedan desafíos por delante para Huawei

La utilización de una litografía más avanzada para la fabricación de chips conlleva la ventaja de reducir el consumo energético manteniendo el mismo diseño, o bien aumentar la velocidad de reloj.

Estas mejoras serían difíciles de lograr si se opta por mantener un proceso de fabricación menos avanzado para construir el chip. Sin embargo, este no es el único desafío al que Huawei se enfrentará en su enfoque hacia la tecnología 3DIC; también debemos considerar dos aspectos adicionales:

- La fabricación de chips mediante el método 3DIC implica la inclusión de pasos adicionales, lo que potencialmente podría duplicar el costo por chip en los casos más desfavorables.

- La disposición de dos chips uno encima del otro resulta en un aumento del calor atrapado, lo que significa que Huawei podría necesitar reducir significativamente la velocidad de reloj para gestionar adecuadamente el problema térmico.

Cabe recordar que las soluciones 3DIC suelen emplearse en chips de bajo consumo, como los utilizados en dispositivos móviles, precisamente debido a esta consideración.

En última instancia, es importante destacar que la propuesta de Huawei en relación con la tecnología 3DIC está en etapa de patente y no se ha presentado aún ningún producto que la utilice.